Verilog Single Cycle MIPS

A single cycle mips processor implementation in verilog.

Github: https://github.com/conneroisu/single-cycle-mips-verilog

singe-cycle-mips-verilog ¶

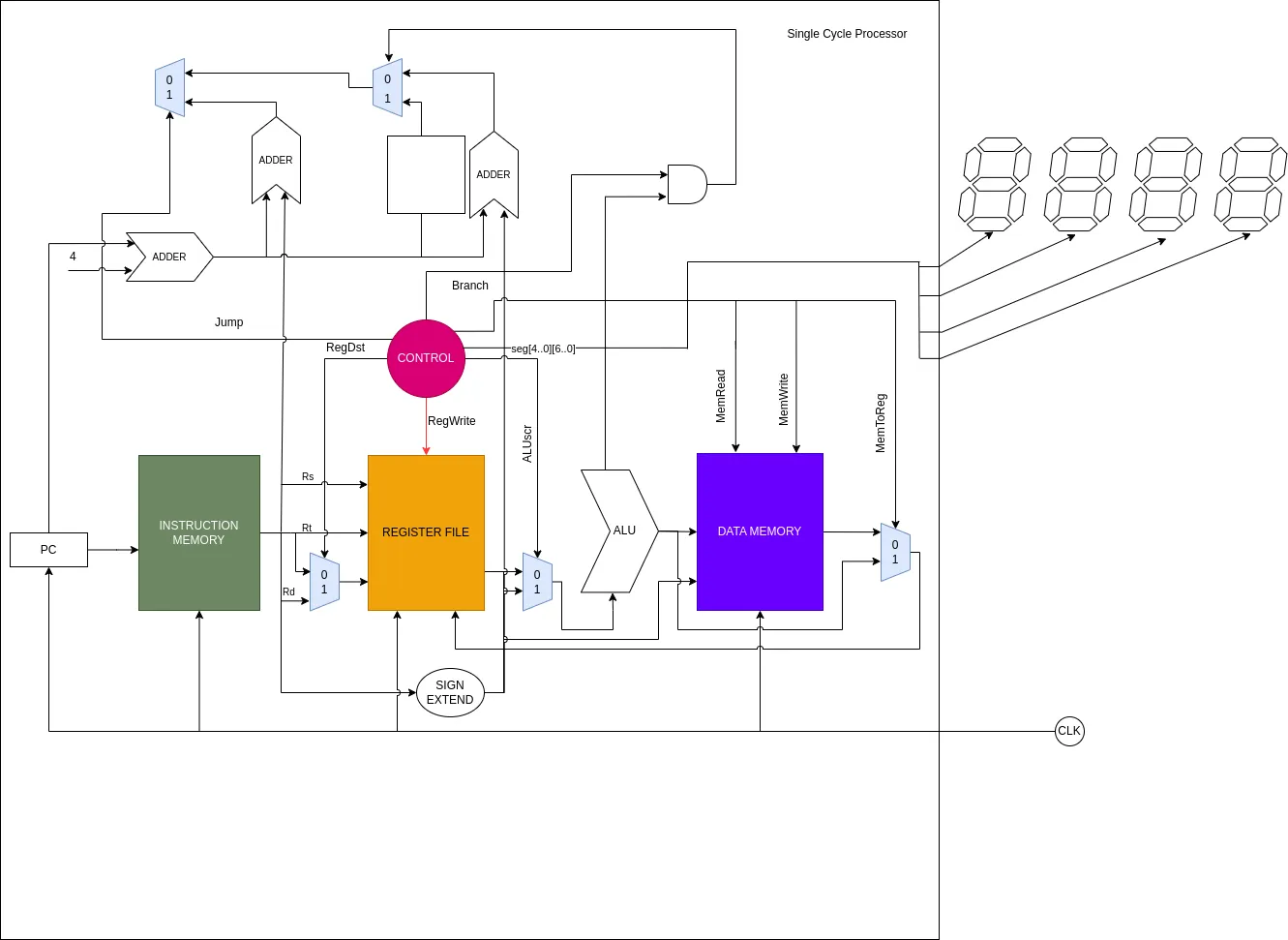

A single cycle mips processor implementation in verilog with reflections from writing a similar single-cycle processor project in vhdl that can execute a subset of the MIPS instruction set and displays the current instruction on the seven segment displays present on the FPGA board. The processor is implemented in Verilog and tested using a test-bench to verify the functionality of the processor. Additionally, the processor is tested on an FPGA board to verify the functionality of the processor.

The processor is able to execute the following instructions: LW SW J ADD ADDI BEQ ADDU SUBU AND ANDI OR ORI SUB NOR BNE SLT

The current instruction being executed will be displayed on the seven segment displays present on the FPGA board. The processor will be implemented in Verilog and tested using a test-bench.

After the processor has been verified using the test-bench, the processor will be tested on an FPGA board to verify the functionality of the processor.

The comparison and contrast of the experience writing the same processor in both Verilog and VHDL will be also included in the final report.

Introduction

The project is a single-cycle MIPS processor that can at a variable speed execute a subset of the MIPS instruction set displaying the current instruction on the seven segment displays present on EP4CE115F29C7 FPGA board.